Intel

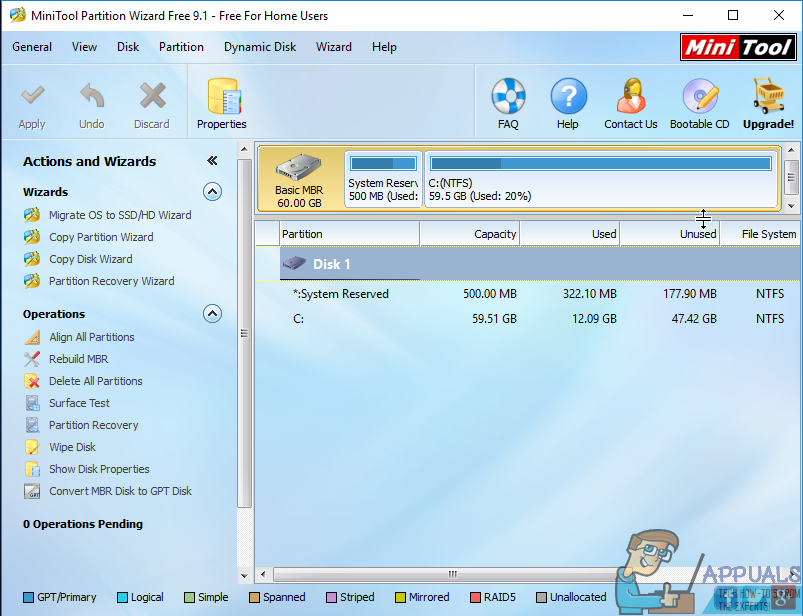

Pangkalan data SiSoftware Sandra telah menjadi salah satu sumber maklumat mengenai perkakasan pengguna. Sekarang, CPU yang belum dirilis dari Intel telah muncul di pangkalan data dengan reka bentuk seni bina yang agak aneh yang boleh membawa kepada sesuatu yang baru dari Intel. Cip 6C dan 12T mungkin kelihatan biasa, tetapi petikan cache melukis gambar yang berbeza sama sekali.

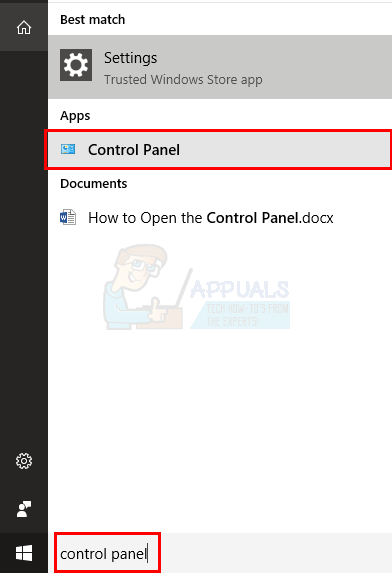

Intel telah melancarkan banyak pemproses enam teras multithread sebagai sebahagian daripada siri teras mereka atau siri Xeon walaupun penyegaran Coffee Lake generasi ke-9 tidak mempunyai pemproses hexacore. Pemproses yang didakwa dalam pangkalan data boleh menjadi pemproses gen ke-9 yang belum dikeluarkan.

Pemproses mempunyai kelajuan jam 2.99GHz, yang tidak setanding dengan pemproses 14nm yang lain kerana prosesnya sangat matang. Adalah standard dengan anggapan pemproses sebenarnya adalah sampel kejuruteraan. Pemproses backported dapat menyokong kelajuan jam yang lebih tinggi walaupun pada tahap inkubasi, tetapi prosesor nampaknya berada pada tahap awal produksi.

Pemproses Hexacore Intel melalui Pangkalan Data SiSoftware

Datang ke bahagian pendedahan yang lebih menarik, pemprosesnya mempunyai sistem cache yang unik. Menurut Wccftech , pemproses mempunyai cache L3 9MB dan cache L2 7.5MB (1.25MB per teras). 1.25MB cache L2 setiap teras bukanlah sesuatu yang Intel boleh capai. Pemproses gen ke-9 mempunyai cache L2 256 KB, CPU Ice Lake 10nm memiliki 512KB, dan siri Core-X menampilkan cache L2 1MB.

Satu-satunya seni bina yang menampilkan 1.25MB cache L2 adalah barisan Tiger Lake yang akan datang. Walau bagaimanapun, cache L3 menjadi anomali kerana ia hanya mempunyai 1.5MB cache L3 per teras, dan pemproses gen ke-9 mempunyai 2MB cache L3. Pemproses Tiger Lake akan menampilkan tetingkap cache L3 yang lebih besar lagi.

Secara keseluruhan, jika kita mengambil kira kelajuan jam dan kutipan cache, kita hanya boleh mengatakan bahawa pemproses yang diduga adalah salah satu pemproses backported (dari Tiger Lake hingga Rocket Lake). Oleh kerana backporting memerlukan pergeseran node, kita mungkin melihat reka bentuk cache yang tidak teratur dan kelajuan jam yang lebih tinggi pada pemproses yang akan datang. Pemproses di tangan boleh menjadi unit pra-pengeluaran awal pemproses backported. Wccftech melaporkan bahawa ia merupakan bahagian pemproses Xeon yang belum dirilis untuk diketengahkan dalam keluarga Ice Lake (E) tahun depan.

Teg 14nm intel Tasik Harimau